# EE/CPRE/SE 491 WEEKLY REPORT 09

#### INTRODUCTION

**Date:** 4/26/2019 **Group Number:** 21

Project Title: Battery-less IoT Devices

Advisor: Dr. Henry Duwe

Clients: Dr. Nathan Neihart, Dr. Daji Qiao

**Team Members:**

Derek Nash - Meeting Scribe, Power Systems Engineer, Test Engineer

Matt Goetzman - RF Systems Engineer, Test Engineer

Mohamed Gesalla - RF Systems Engineer, Test Engineer

Adithya Basnayake – Report Manager, Power Systems Engineer, Test Engineer

Mohammed-Al-Mukhaini – Meeting Facilitator, Embedded Systems Engineer, Test Engineer

Bradley Rhein – Embedded Systems Engineer, Test Engineer

## PAST WEEK ACCOMPLISHMENTS

#### **Embedded Systems Team**

In addition to working on the project plan, the embedded team began using EnergyTrace during code development to get an idea of how much power and energy the MCU will consume during various modes of operation. This tool will be extremely helpful in giving the other teams of the power requirements for the MCU, and will give the entire team an idea of how long the device must wait to fully charge. We also learned how to properly store non-volatile data with FRAM.

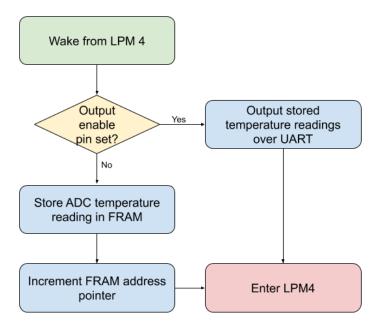

With a proper development board, we now can implement and test our software. The below figure is a flowchart for our program that we will implement.

#### RF and Antenna Team

This week, most of the time was dedicated to making the project plan and prepare for presentation for next week. More on the technical side, as the team is finalizing the patch antenna design, we spent some time this week looking into how our etching process will be affected by the PCB substrate parasitics. From our research, we found the right equations with the right dielectric constant that will allow us to calculate the capacitive and inductive parasitic for our FR-4 board.

Equations as shown below:

$$C = \frac{kA}{11.3d} \,\mathrm{pF} \tag{1}$$

For calculating the parasitic capacitance

Inductance =

$$0.0002L \left[ ln \frac{2L}{(W+H)} + 0.2235 \left( \frac{W+H}{L} \right) + 0.5 \right] \mu H$$

For calculating Strip Inductance

$$L = 2T \left[ \ln \frac{4T}{d} + 1 \right] nH$$

For calculating parasitic Inductance

# **Power Circuit Team**

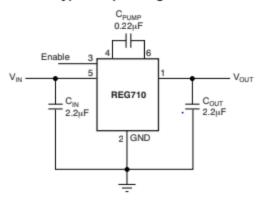

The power circuit team contributed to making the project plan, design document, and presentation. Research was done into the REG710xx series of low-power voltage regulators.

## **Typical Operating Circuit**

Figure xx: schematic of the voltage regulator

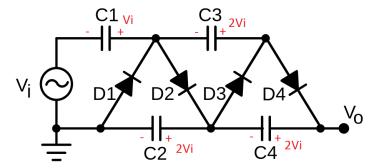

The team also did a circuit analysis on the cockcroft Walton multiplier under ideal conditions. We decided to fo with 2 stages in this multiplier because it is happy medium between stepping up the voltage and output voltage drop.

Figure #: Cockcroft Walton multiplier

The voltage output is calculated using the following equation

$2nV_{MAX}$  this is ideal voltage output  $2nV_{MAX}$  -  $2 V_0$  this is real voltage output

$$\Delta V_o = \frac{(4n^3 + 3n^2 - n)}{6} \frac{I_o}{fC}$$

, n = number of stages

## PENDING ISSUES

The team needs to finish the design document and presentation file, give their presentation, and take steps to plan for their progress next semester.

## INDIVIDUAL CONTRIBUTIONS

| Team Member              | Contribution                                                                                                                                               | Weekly<br>Hours |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Derek Nash               | Helped update Project Description. Researched a low-power voltage regulator.                                                                               | 5               |

| Matt Goetzman            | Worked on Final Project Plan. Researched impedance matching.                                                                                               | 5               |

| Mohamed Gesalla          | Looking into the etching process of the antenna into the PCB board as well as the effects of parasitics. And worked on the final draft of the project plan | 6               |

| Adithya Basnayake        | Updated the project plan. Did a circuit analysis on the Cockcroft Walton multiplier                                                                        | 5               |

| Mohammed-Al-<br>Mukhaini | Produces new results of using Energytrace to optimize our understanding in energy consumption. Created some application for Fram,                          | 6               |

| Bradley Rhein            | Learned how to properly store & preserve data with FRAM, learned how to take EnergyTrace measurements, and and worked on the design document.              | 6               |

#### PLANS FOR THE UPCOMING WEEK

The team plans to give their presentation on Monday, 4/29 and work on the design document.

## SUMMARY OF WEEKLY ADVISOR MEETING

Dr. Duwe talked about the importance of having prototypes, even in the design phase. He also gave some advice on our project document; mainly, that the requirements should be more specific, such as charge time. During this meeting we also talked about the issues with the voltage regulator circuit REG710xx and the need for a kick starter circuit for the voltage regulator.